Durchgesickerte Informationen aus AMDs internen Dokumenten enthüllten die Codenamen Nirvana und Morpheus für Zen5 bzw. Zen6. Es wird erwartet, dass Zen6 die Anzahl der Kerne pro Chiplet auf bis zu 32 Kerne erhöht und die Unterstützung für hochpräzise Gleitkommaoperationen verbessert. Diese werden für KI- und Machine-Learning-Anwendungen notwendig sein.

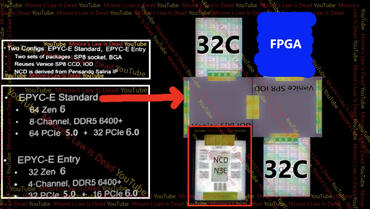

Aus dem Leak geht hervor, dass AMD eine EPYC-E Produktserie entwickelt. Das "E" im Namen soll vermutlich für Edge stehen. Damit richtet sie sich vermutlich an Telekommunikations- und Edge-Computing-Systemanbieter, die eine geringere Kernzahl und einen niedrigeren Stromverbrauch erfordern. Das Diagramm zeigt einen Venice SP8 IOD mit 32 Zen6-Kernen und deutet damit auf ein spezielles CPU-Design hin, das auch Network Compute Dies auf Basis des Pensando Salina-Designs enthalten könnte.

Die EPYC-E Serie wird voraussichtlich in zwei Varianten erscheinen: eine Standard Edition mit 64 Zen6-Kernen und eine Entry Variante mit 32 Kernen. Die Standard-Edition wird voraussichtlich Octa-Channel-DDR5-6400-Speicher und eine Kombination aus 64 PCIe Gen5- und 32 PCIe Gen6-Schnittstellen unterstützen, während die Entry-Variante wahrscheinlich Quad-Channel-Speicher und weniger PCIe-Lanes bieten wird.

Außerdem könnte AMD neben Sockel SP7 einen neuen Sockel SP8 verwenden, um verschiedene CPUs der EPYC-Serie aufzunehmen. Es wird vermutet, dass der Sockel SP8 für die kommenden Siena- und Sorano-Nachfolger vorgesehen ist.

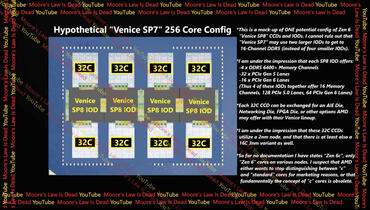

Das MLID-Modell eines möglichen Zen6 EPYC-Prozessors für den Sockel SP7 zeigt, wie ehrgeizig die Pläne von AMD sind. Das Unternehmen scheint nicht mehr zwischen Zen6- und potenziellen Zen6c-Kernen zu unterscheiden, möglicherweise aufgrund einer strategischen Veränderung oder weil solche Kerne nicht geplant sind. Das neue Design könnte bis zu 256 Zen6-Kerne enthalten, was eine deutliche Steigerung gegenüber den aktuellen Zen4- und den kommenden Zen5-Kernen bedeutet.