Panmnesia CXL-Protokol (Bild © Panmnesia)

Panmnesia CXL-Protokol (Bild © Panmnesia)

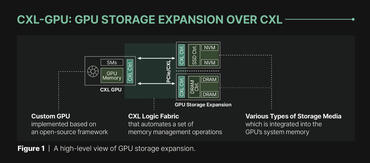

Die innovative CXL-IP von Panmnesia ermöglicht es GPUs, ihre Speicherkapazität durch die Nutzung von externem DRAM oder SSDs zu erweitern und so die Lücke zwischen eingebautem HBM und zusätzlichen Speicherressourcen effektiv zu schließen. Dies wird durch PCIe-Verbindungen erreicht, die Kompatibilität und einfache Akzeptanz bei den Verbrauchern gewährleisten.

Herkömmliche KI-Beschleuniger sind jedoch nicht mit den notwendigen Subsystemen ausgestattet, um CXL zur Speichererweiterung anzuschließen und zu nutzen. Bestehende Lösungen wie Unified Virtual Memory (UVM) sind oft zu langsam, was ihre Effektivität untergräbt. Um dieses Problem zu lösen, hat Panmnesia einen CXL 3.1-kompatiblen Root Complex Chip entwickelt, der über mehrere Ports verfügt, die die GPU über einen PCIe-Bus mit dem externen Speicher verbinden. Der Host-Managed Device Memory (HDM)-Decoder spielt eine entscheidende Rolle bei der Verwaltung der Speicherzuweisung und der Übersetzung.

Die Benchmarks von Panmnesia zeigen, dass ihre Lösung mit dem Namen CXL-Opt die Prototypen der Branchenriesen Samsung und Meta, die als "CXL-Proto" bezeichnet werden, deutlich übertrifft. CXL-Opt wies eine bemerkenswert niedrige Latenzzeit auf, die im zweistelligen Nanosekundenbereich lag, im Vergleich zu CXL-Proto, das 250 ns benötigte. Außerdem ist die Ausführungszeit von CXL-Opt der von UVM weit überlegen und erreicht eine 3,22-mal höhere IPC-Leistung.

Diese innovative Lösung von Panmnesia bietet einen vielversprechenden Zwischenschritt zwischen dem Stapeln weiterer HBM-Chips und dem Übergang zu einer effizienteren und skalierbaren Speicherlösung. Als einer der Pioniere bei der Entwicklung einer funktionalen CXL-IP wird Panmnesia erhebliche Vorteile erzielen, wenn sich seine Lösung auf dem Markt durchsetzt.