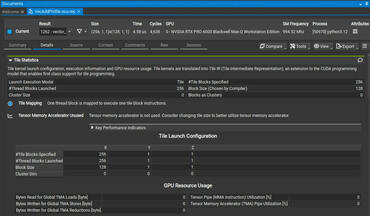

Unter dieser Abstraktion befindet sich ein neues CUDA Tile IR, das als virtueller Befehlssatz fungiert, den die Toolchain auf Threads, Speicherhierarchien und Tensor Core-Operationen auf aktuellen und zukünftigen Architekturen reduziert.

Dieser Schritt zeigt, wie wichtig Tensoren in der modernen KI und HPC sind. Die neuesten Chips von NVIDIA kombinieren Tensor-Kerne mit Tensor-Speicherbeschleunigern (TMA), um Matrixberechnungen und Datenbewegungen zu beschleunigen, aber um die Leistung voll auszuschöpfen, braucht man normalerweise genaue Kenntnisse der Hardware-Details. Das Ziel von CUDA Tile ist es, das Algorithmusdesign von der Mikroarchitektur zu trennen, damit optimierte Kernel mehrere GPU-Generationen mit minimalen Änderungen überstehen und trotzdem zu einer effizienten, hardwarebewussten Ausführung kompiliert werden können.

Wie CUDA Tile zu PTX passt

Seit mehr als einem Jahrzehnt ist PTX die Portabilitätsschicht von CUDA für SIMT-Programme. CUDA Tile IR erweitert dieses Konzept auf tile-native Programme: Entwickler konzentrieren sich auf Tiling-Strategien, während der Compiler/die Laufzeitumgebung die Zuordnung zu Threads, gemeinsam genutztem und globalem Speicher sowie Tensor-Einheiten verwaltet. Diese Grundlage öffnet auch die Tür für domänenspezifische Sprachen und Compiler höherer Ebene, die auf NVIDIA-GPUs abzielen, ohne die Low-Level-Planungs- und Datenbewegungslogik neu implementieren zu müssen.

Neues in CUDA 13.1

Neben CUDA Tile bringt die Version einige bemerkenswerte Updates mit sich:

- Runtime-API-Exposure von Green Contexts, Erweiterung der Management-Hooks für erweiterte Laufzeitsteuerung.

- cuBLAS-Emulation für einfache und doppelte Genauigkeit, Verbesserung der Entwickler-Workflows und der Abdeckung in Testumgebungen.

-

Ein komplett überarbeiteter CUDA-Programmierleitfaden, der die Dokumentation an das neue kachelbasierte Modell und aktualisierte Best Practices anpasst.