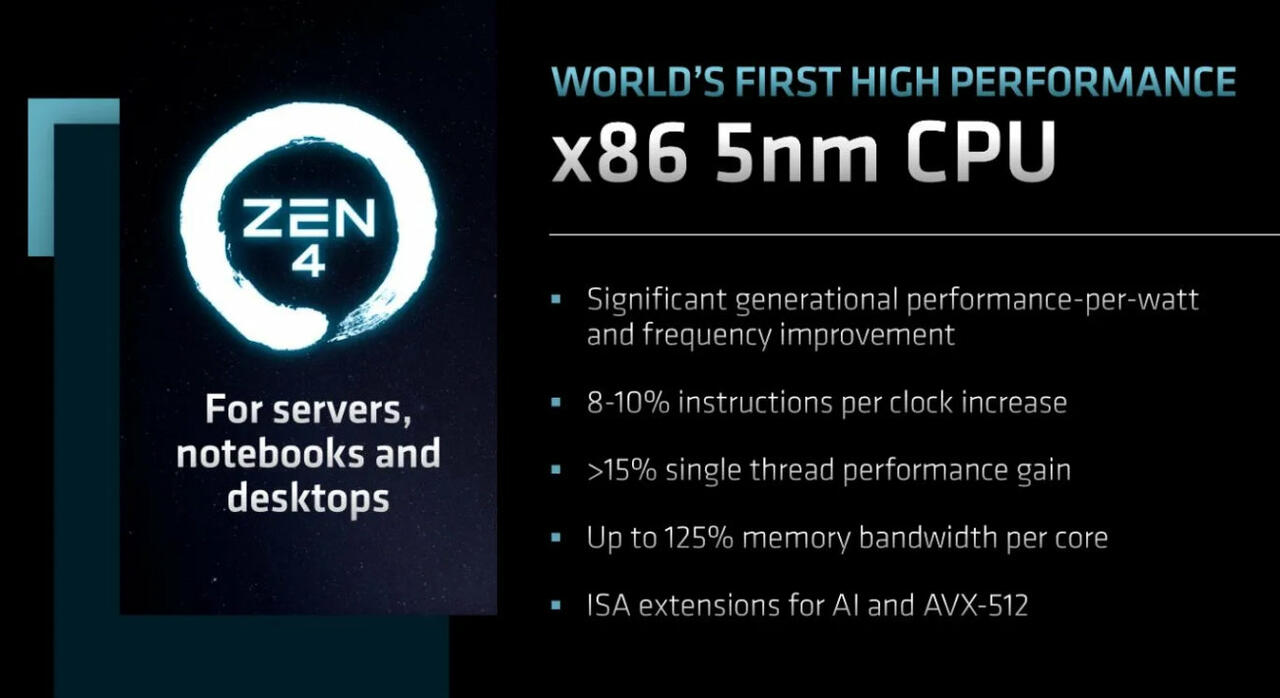

AMD Ryzen Roadmap Zen5 und Zen4 (Bild © AMD)

AMD Ryzen Roadmap Zen5 und Zen4 (Bild © AMD)

Traditionell bringt AMD Updates für die Compilerunterstützung nach der Einführung einer neuen Produktlinie auf den Markt. Der frühe Start der Zen5-Patches, noch vor der offiziellen Veröffentlichung des Produkts, stellt jedoch eine bemerkenswerte Beschleunigung von AMDs Compiler-Enablement-Prozess dar. Da die Veröffentlichung von GCC 14 für März und April erwartet wird, was mit dem jährlichen Update-Zyklus des Compilers übereinstimmt, deutet AMDs Timing darauf hin, dass das Unternehmen die Softwarekompatibilität und -leistung lange vor dem Debüt von Zen5 optimieren möchte.

Die Zen5-Architektur wird voraussichtlich noch in diesem Jahr auf den Markt kommen und die Desktop-orientierte Granite Ridge-Serie sowie potenzielle mobile Angebote der Strix Point-Serie einführen. Die ersten Patches für Zen5 bieten Unterstützung für mehrere neue Befehle, darunter AVXVNNI, MOVDIRI, MOVDIR64B, AVX512VP2INTERSECT und PREFETCHI. Einige dieser Befehle, wie z.B. AVX-512 VP2INTERSECT, MOVDIRI und MOVDIR64B, waren bereits in Intels Tiger Lake-Serie vorhanden, sind aber neu in AMDs Produktpalette. Die Aufnahme von PREFETCHI, das voraussichtlich mit Intels Granite Rapids debütieren wird, und AVX-VNNI, vergleichbar mit AVX512-VNNI mit VEX-Kodierung, unterstreicht AMDs Engagement für die Verbesserung von Verarbeitungsfähigkeiten und Effizienz.

- znver5: AMD Family 1ah core based CPUs with x86-64 instruction set support. (This supersets BMI, BMI2, CLWB, F16C, FMA, FSGSBASE, AVX, AVX2, ADCX, RDSEED, MWAITX, SHA, CLZERO, AES, PCLMUL, CX16, MOVBE, MMX, SSE, SSE2, SSE3, SSE4A, SSSE3, SSE4.1, SSE4.2, ABM, XSAVEC, XSAVES, CLFLUSHOPT, POPCNT, RDPID, WBNOINVD, PKU, VPCLMULQDQ, VAES, AVX512F, AVX512DQ, AVX512IFMA, AVX512CD, AVX512BW, AVX512VL, AVX512BF16, AVX512VBMI, AVX512VBMI2, AVX512VNNI, AVX512BITALG, AVX512VPOPCNTDQ, GFNI, AVXVNNI, MOVDIRI, MOVDIR64B, AVX512VP2INTERSECT, PREFETCHI and 64-bit instruction set extensions.)

Die Zen5-Patches deuten auf einen einheitlichen Befehlssatz für die gesamte Zen5-Produktfamilie hin, was bedeutet, dass sowohl die Standard- als auch die energieeffizientere Zen5c-Variante diese fortschrittlichen Befehle unterstützen werden. Dieser umfassende Ansatz für die Kompatibilität der Befehlssätze stellt sicher, dass AMDs kommende CPUs in verschiedenen Computerumgebungen eine optimale Leistung bieten werden.

Während in dieser ersten Aktivierungsphase bestimmte Scheduling-Codes von Zen4 als Platzhalter portiert wurden, wird erwartet, dass die AMD-Ingenieure eine verfeinerte Version speziell für Zen5 bereitstellen. Eine offene Frage ist die Unterstützung von Zen5 in LLVM/Clang-Compilern, für die noch keine Patches zur Verfügung stehen.