AMD Strix Halo High-End-APU Renderbilder (Bild © @Olrak_29 auf X)

AMD Strix Halo High-End-APU Renderbilder (Bild © @Olrak_29 auf X)

Was über Strix Halo APUs geleakt wurde

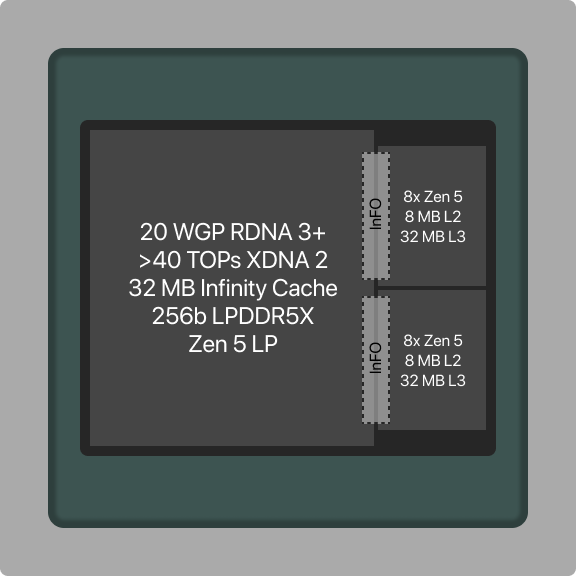

Die AMD Strix Halo APUs nutzen ein Chiplet-Design mit bis zu drei Dies: zwei Core Complex Dies (CCDs) und ein Graphics Compute Die (GCD). Dieser Aufbau umfasst bis zu 32 Threads und bietet maximal 16 MB L2-Cache und 64 MB L3-Cache. Der GCD ist der größte Die und integriert alle I/O-Blöcke, einschließlich einer XDNA 2 AI Neural Processing Unit (NPU) mit über 40 TOPs, 32 MB Infinity Cache und 256-Bit LPDDR5X Speicher. Außerdem beherbergt der GCD Zen 5 Low-Power-Kerne, die über eine Infinity Fabric-Verbindung mit den dualen Zen 5 CCDs verbunden sind.

Die Strix Halo APUs verfügen über die RDNA 3+ Architektur mit 20 Workgroup-Prozessoren (WGPs) oder 40 Compute Units. Um die integrierte High-End-GPU zu unterstützen, gibt es zusätzlich 32 MB MALL-Cache, um Bandbreitenengpässe zu vermeiden.Weitere bemerkenswerte Spezifikationen sind die Unterstützung von bis zu LPDDR5X-8000-Speicher, eine KI-"XDNA 2"-NPU mit über 70 TOPs und insgesamt 16 PCIe Gen4-Lanes.Die APUs haben eine Thermal Design Power (TDP) von 55W bis 130W und orientieren sich an den neuesten FP11-Plattformen.

Sie unterstützen außerdem eDP (DP2.1 HBR3), externes DP (DP2.1 UHBR10), USB-C Alt-DP (DP2.1 UHBR10) und USB4 Alt-DP (DP2.1 UHBR10). Die Strix Halo wird außerdem bis zu DP2.1 UHBR20 unterstützen.

Es wird erwartet, dass AMD sein Zen 5 "Ryzen" CPU-Portfolio der nächsten Generation während seiner Keynote auf der Computex 2024 offiziell ankündigt und vorstellt. Da die Markteinführung für die zweite Jahreshälfte 2024 erwartet wird, dürften bald weitere Informationen veröffentlicht werden, die einen deutlichen Leistungssprung für High-End-Laptops versprechen.