CopperLink - PCIe-Express über Kabel (Bild © PCI-SIG )

CopperLink - PCIe-Express über Kabel (Bild © PCI-SIG )

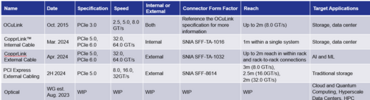

CopperLink wird die Konnektivität in modernen Speichersystemen, Rechenzentren und KI-Infrastrukturen neu definieren und zielt zwar nicht direkt auf den Verbrauchermarkt ab, hat aber möglicherweise einen großen Einfluss auf diesen. Die Technologie unterstützt PCIe 5.0 und 6.0 mit Signalgeschwindigkeiten von 32 bzw. 64 GT/s, und es gibt bereits Pläne für eine PCIe 7.0-Spezifikation, die diese Raten auf 128 GT/s verdoppeln könnte.

Anschluss über CopperLink-Kabel

CopperLink-Kabel gibt es in zwei Ausführungen: intern und extern. Die internen Kabel mit dem SNIA SFF-TA-1016-Anschluss können Komponenten innerhalb eines Systems verbinden, z. B. Motherboard und Add-in-Karten oder Chip-to-Chip-Konfigurationen, und haben eine maximale Länge von 1 Meter. Die externen Kabel verwenden den SNIA SFF-TA-1032-Stecker, der längere Verbindungen von bis zu 2 Metern ermöglicht, ideal für die Verbindung von CPUs mit Speicher und Beschleunigern in verschiedenen Racks.

Diese Technologie verspricht nicht nur die Datenübertragung und Effizienz in technischen und industriellen Umgebungen zu verbessern, sondern hat auch das Potenzial, sich auf den Verbrauchermarkt auszuwirken, da sich externe Grafikprozessoren und KI-Beschleuniger im Heimcomputerbereich immer mehr durchsetzen. Obwohl CopperLink auf die Industrie ausgerichtet ist, könnte es sich schnell durchsetzen und mit Thunderbolt 5 konkurrieren, das eine einfachere Verbindung über USB Typ-C und eine Bandbreite von bis zu 120 Gbit/s bietet. Wenn die PCI-SIG diese vielversprechende Technologie weiterentwickelt, könnten die Grenzen zwischen Industrie- und Verbraucheranwendungen zunehmend verschwimmen.

Spezifikation des internen CopprLink-Kabels

- Unterstützt PCIe 5.0 und 6.0 Technologie mit 32.0 und 64.0 GT/s

- Beinhaltet den SNIA SFF-TA-1016 Steckerformfaktor

- Maximale Reichweite von 1 m innerhalb eines einzelnen Systems

- Beispielimplementierungen umfassen Motherboard-to-Add-in-Card, Motherboard-to-Backplane, Chip-to-Chip und Add-in-Card-to-Backplane in einem eigenständigen Serverplattformknoten

- Zu den Zielanwendungen gehören Speicher- und Rechenknoten im Rechenzentrum

Spezifikation des externen CopprLink-Kabels

- Unterstützt PCIe 5.0 und 6.0 Technologie mit 32,0 und 64,0 GT/s

- Beinhaltet den SNIA SFF-TA-1032 Steckerformfaktor

- Maximale Reichweite von bis zu 2 m bei Rack-to-Rack-Verbindungen

- Beispiele für Implementierungen sind CPU-to-Storage, CPU-to-Memory, CPU-to-Accelerator und - Accelerator Fabrics in disaggregierten Serverplattformknoten

- Zu den Zielanwendungen gehören Speicher- und KI/ML-Anwendungsfälle im Rechenzentrum